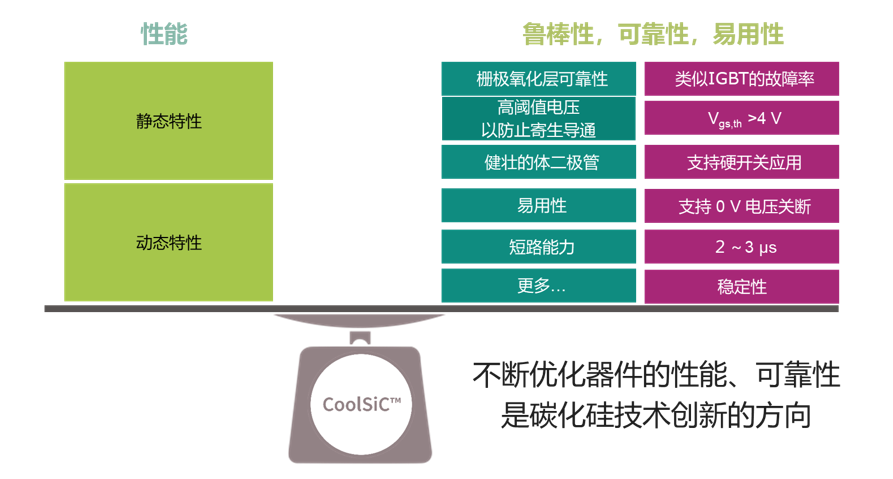

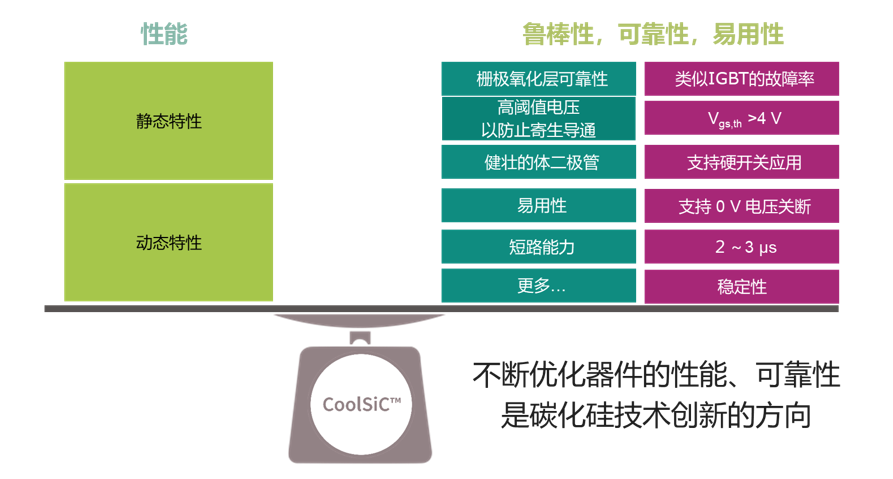

碳化矽功率半導體在光電、充電、電動車等產業得到了廣泛應用,其潛力毋庸置疑。然而,從目前高功率碳化矽MOSFET來看,仍存在一個難題:即如何實現平衡性能、穩健性、可靠性和易用性的設計。比導通電阻是衡量SiC MOSFET技術先進性的關鍵參數,但其它標準,例如可靠性,也是限制裝置表現的重要因素。對於不同的應用,導通電阻與可靠性之間的折衷也略有差異。因此,合理的裝置定義應確保設計彈性,以滿足不同的任務需求,無需大量設計工作和設計佈局變更。

May . 2025

分享至

碳化矽功率半導體在光電、充電、電動車等產業得到了廣泛應用,其潛力毋庸置疑。然而,從目前高功率碳化矽MOSFET來看,仍存在一個難題:即如何實現平衡性能、穩健性、可靠性和易用性的設計。比導通電阻是衡量SiC MOSFET技術先進性的關鍵參數,但其它標準,例如可靠性,也是限制裝置表現的重要因素。對於不同的應用,導通電阻與可靠性之間的折衷也略有差異。因此,合理的裝置定義應確保設計彈性,以滿足不同的任務需求,無需大量設計工作和設計佈局變更。

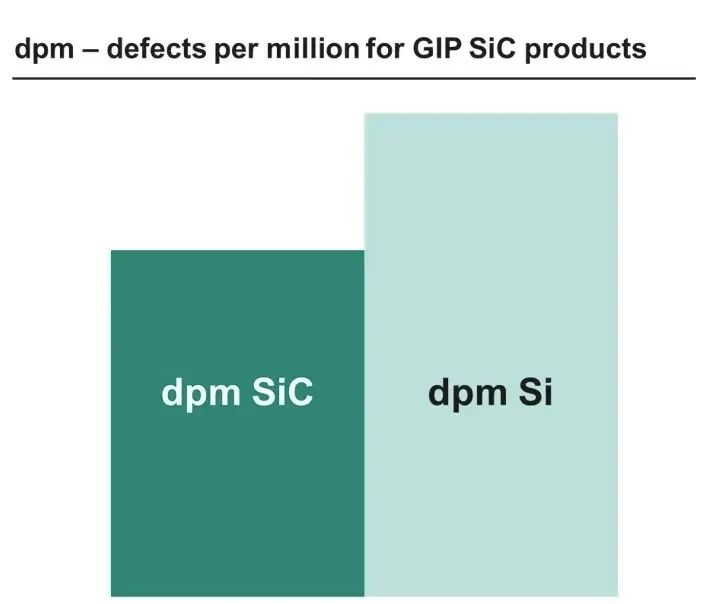

談到可靠性,人們往往會認為SiC不如IGBT,但事實並非如此。在碳化矽MOSFET中,閘極氧化層可靠性和宇宙射線故障率共同決定了裝置FIT率。英飛凌透過研究已售出的2300萬片的CoolSiC™ MOSFET晶片的故障率 ,並與成熟的矽IGBT相比較,可以發現,CoolSiC™的每百萬分之一故障率更低。包括模組和分立裝置的所有產品系列都是如此。

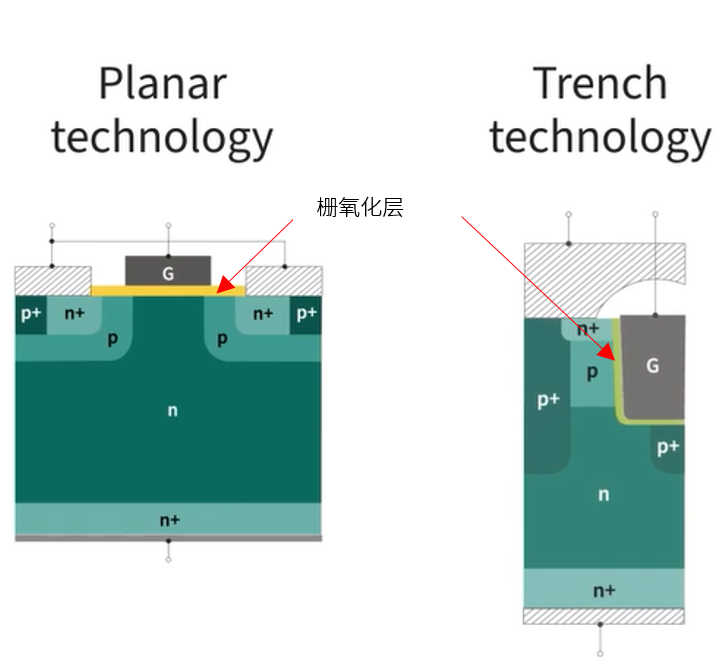

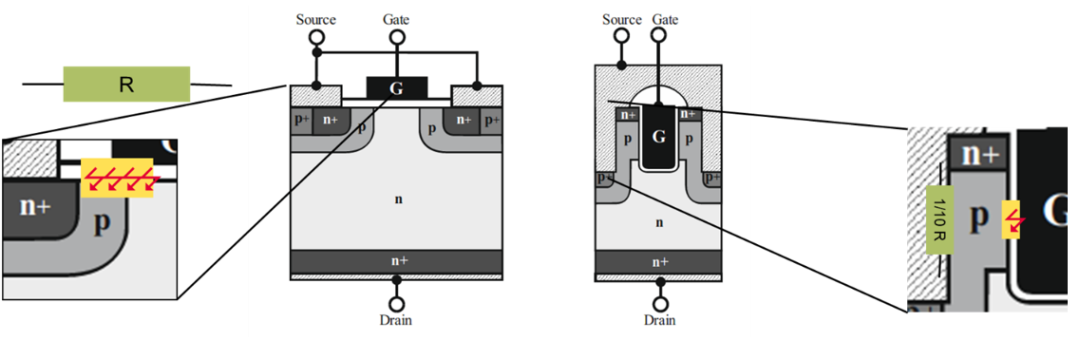

SiC MOSFET主要結構有平面型planar和溝槽型trench兩種。儘管業界流行的說法溝槽柵型裝置在可靠性方面難度較高,但英飛凌使用獨特的辦法解決了這個問題。

我們觀察平面型和溝槽型的裝置結構,都能夠發現在閘極(G)與矽片之間,有一層薄薄的氧化層,我們稱之為柵極氧化層。別看這層氧化層的厚度不足100nm,卻在SiC MOSFET的設計中,起著十分重要的作用,關係到裝置的閾值、導通電阻、閘極電壓範圍、可靠性等諸多參數。

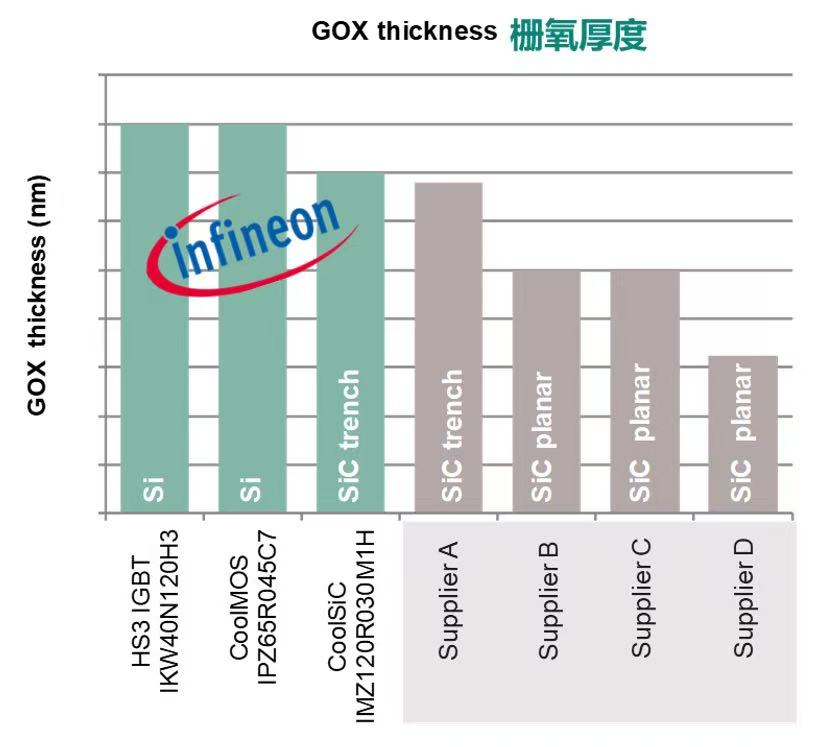

我們比較了各廠家元件柵氧化層厚度,發現英飛凌SiC MOSFET閘氧化層厚度是所有SiC元件中最厚的,與矽基IGBT元件差不多,而平面閘極SiC MOSFET閘氧化層厚度僅有40~50nm。

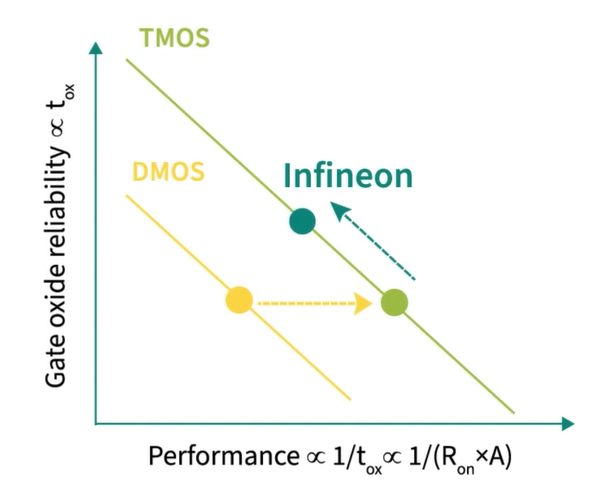

閘極氧化層厚度在SiC MOSFET可靠性和性能的權衡中起著重要作用。 SiC的可靠性隨柵氧厚度上升而呈指數級上升趨勢,而導通電阻僅略微上升,因而CoolSiC™ MOSFET實現了性能與可靠性的最佳平衡。使用較厚的閘極氧化層,只需犧牲很少的性能,就能換取可靠性的大幅提升。不論平面型DMOS,還是溝型TMOS的SiC MOSFET都遵循這樣的權衡曲線。

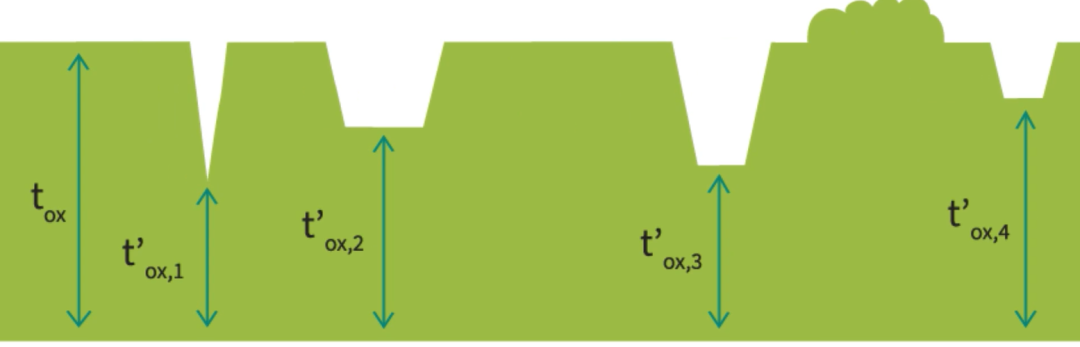

為何我們格外關注閘極氧化層厚度? SiC 材料上形成的二氧化矽層,比矽材料上的二氧化矽有更多的缺陷。直觀來看,這些缺陷的影響方式是使閘氧化層局部變薄,且失效風險更高。為了消除存在此類缺陷的裝置,最大程度上降低閘極氧化層缺陷對裝置性能的影響,保證裝置的長期可靠性,英飛凌對閘極氧化層實施篩選,即在生產之後對裝置施加較高的閘極電壓,如果閘極氧化層中含有缺陷,那麼該點的電場就會高於二氧化矽元件所承受的臨界電場,導致有缺陷的雜訊電場,導致有缺陷的晶片或效能下降,而無瑕疵的裝置則不會受到影響,

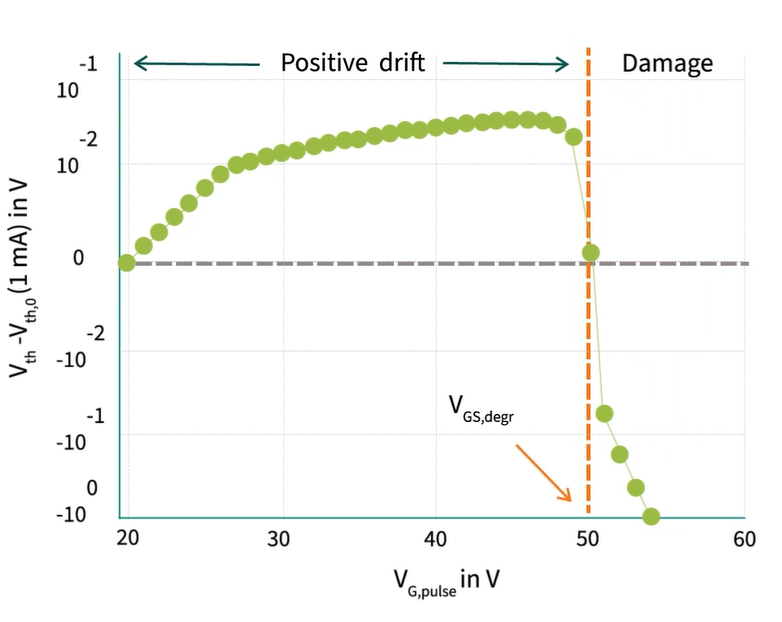

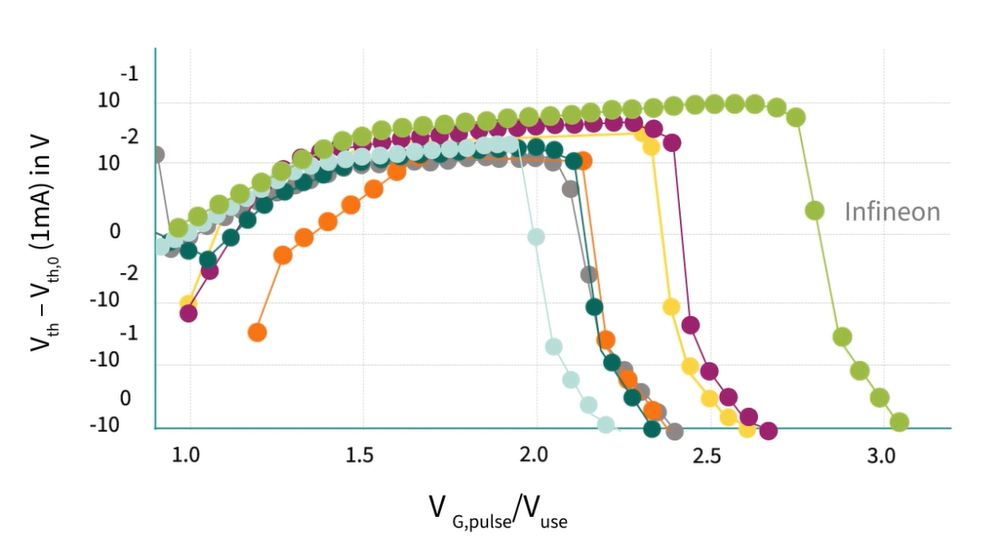

篩選時所採用的電壓與額定閘極電壓的比例對於篩選的效率至關重要,並且在很大程度上取決於閘極氧化物的整體厚度。在這張圖中,我們可以看到X軸代表短時脈衝電壓,Y軸代表閾值電壓的變化,當向碳化矽MOSFET晶片施加閘極-源極電壓時,會引入一個短時的正閘極應力,導致閾值電壓發生微小的正移,一旦閘極電壓超過臨界值,就會發現閾值電壓開始顯著下降,此時,氧化物內部達到臨界電場強度,引發內部撞擊電離,這意味著,當電荷載子在氧化物中被強烈加速時,它可以激活新的電荷載流子,並開始產生新的缺陷,因此,如果施加的電壓高於這個臨界閘極-源極電壓,篩選過程就會進一步損壞閘極氧化物。

為了更清楚地說明問題,我們來比較兩種不同的閘極氧化物,假設兩者俱有相同的缺陷,由於臨界電壓取決於閘極氧化物的整體厚度。 DMOS元件的柵極氧化層較薄,當電壓升高時,較早達到臨界電場,因此,對較薄氧化物的裝置施加的篩選電壓要低得多,所以一些具有嚴重臨界缺陷的裝置仍然能通過篩選,這對於應用是十分不利的。對於較厚的氧化物,因為能夠施加更高的篩選電壓,更多的缺陷被高電壓篩選出來,而我們只向客戶交付篩選後未顯示任何損壞或變化的裝置。透過在終測中剔除有缺陷的裝置,客戶面臨的潛在可靠性問題就能被英飛凌遭受的微小良率損失所取代。

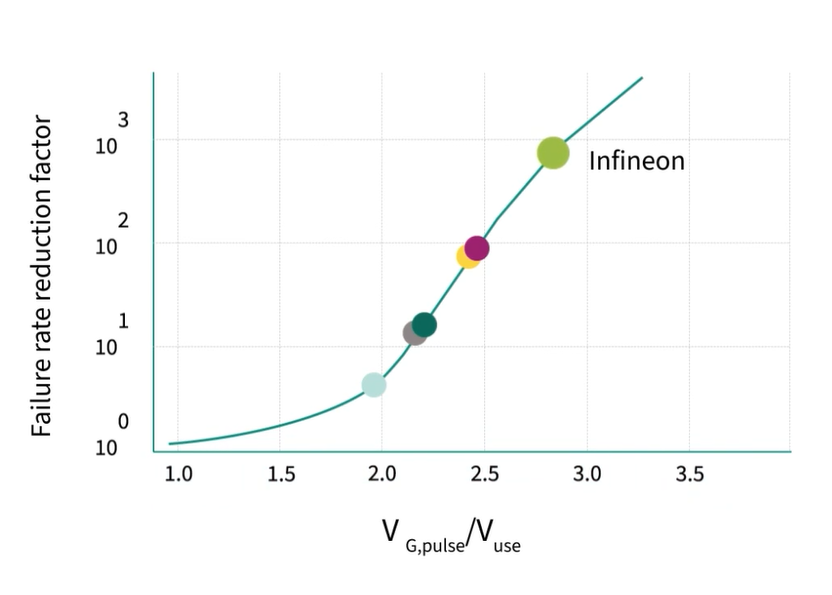

讓我們再比較一下不同供應商的篩選能力,如圖所示:

為確保比較的公平,應使用建議使用電壓和脈衝電壓之間的比率,從圖中可以清楚地看到,英飛凌裝置具有最高的閘極電壓,以脈衝閘極電壓和使用閘電壓比為標準,這種改進的篩選可能性對失效率降低係數的影響更加明顯,到目前為止,英飛凌元件的故障率降低極十倍™是最高的,比其他重量降低十倍,這使得我們的低壓差。

透過剛才的闡述,我們已經了解到,溝槽閘結構具有更厚的閘極氧化層,因此能採用更高的篩選電壓。那為什麼平面型結構普遍較低?

這是因為碳化矽在形成閘極氧化層的時候,SiC-SiO2界面之間存在較高態密度與氧化層陷阱,導致通道電阻比較高。打個比方,電子在通道上流過,好比汽車在公路上行駛。公路路面狀況越好,則車速越快;路面若全是坑,再好的車速度也起不來。

好在SiC是一種各向異性的晶體,不同的晶面上形成SiC-SiO2界面缺陷率是不同的。垂直晶面上SiC-SiO2界面態密度與氧化層陷阱較低,界面電氣性能較好。溝槽型的SiC MOSFET好比避開了坑洞的路面,在地下挖了一條光滑的隧道,因此電子遷移率更高,通道電阻更低。

為降低通道電阻,平面型SiC MOSFET往往採用較高的閘極驅動電壓,或是很薄的閘極氧化層,這使得閘極氧化層上的電場強度升高,較高的電場會加速器件老化,而這正是導致最終FIT率的主要原因。但與平面柵型相比,溝槽柵型碳化矽MOSFET的通道電阻小很多,也就是說,即使採用較厚的柵極氧化層,仍能得到非常好的性能。

此外,決定任一技術閾值電壓變化等的重要參數,如通道尺寸和摻雜,在垂直結構中都能更容易、更準確地控制。

英飛凌著手開發碳化矽功率元件已有30年的歷程。英飛凌在設計之初就決定開發溝槽閘極結構,而非更容易實現的平面閘設計,儘管開發溝槽閘需要更高深的工藝知識。英飛凌透過選擇具有較厚閘極氧化物的溝槽閘MOSFET,成功地將其可靠性特性融入元件設計中,從而實現了有效的缺陷篩選,而這一點是採用較薄極氧化物的其他裝置設計所無法實現的,該決策使英飛凌實現了超越成熟矽技術的高可靠性,同時不會對關鍵性能參數產生負面影響。