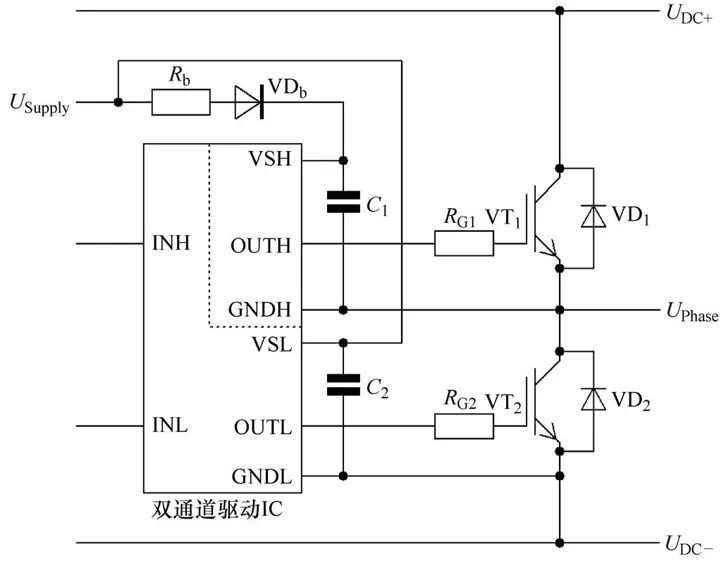

驅動電路設計是功率半導體應用的困難點,涉及功率半導體的動態過程控制及元件的保護,實踐性很強。為了方便實現可靠的驅動設計,英飛凌的驅動整合電路附帶了一些重要的功能,本系列文章講詳細說明如何正確理解和應用這些功能。

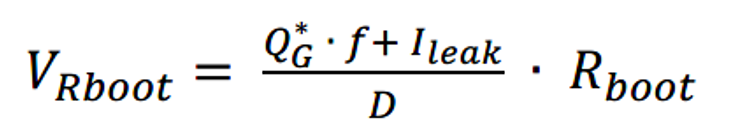

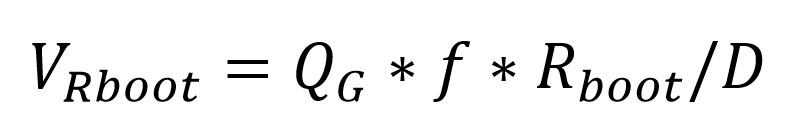

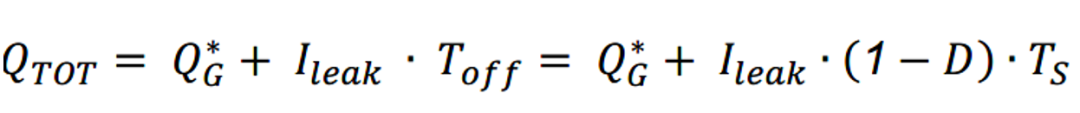

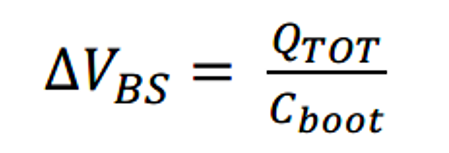

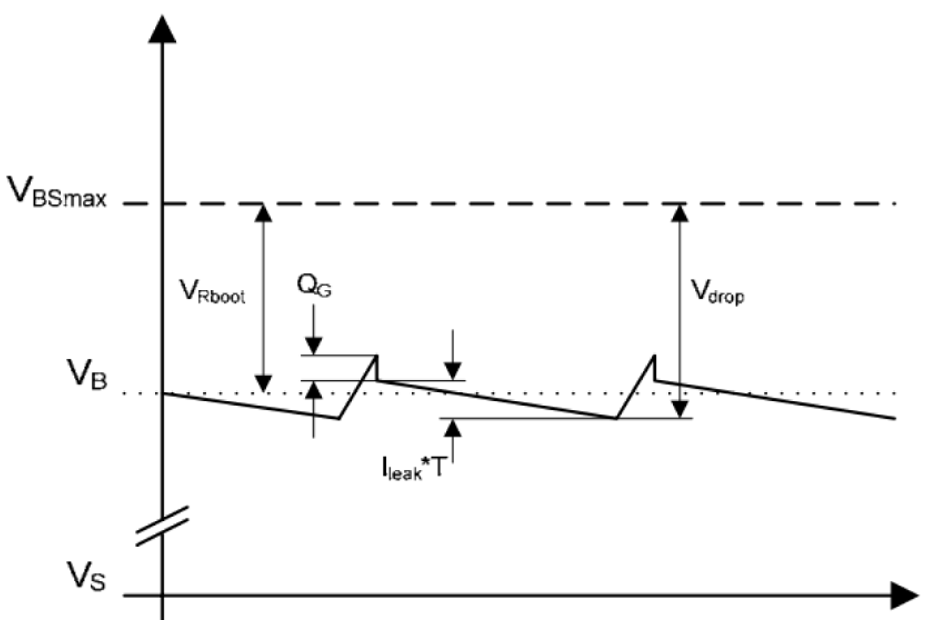

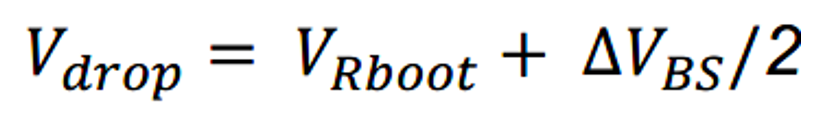

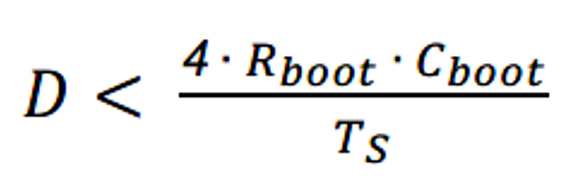

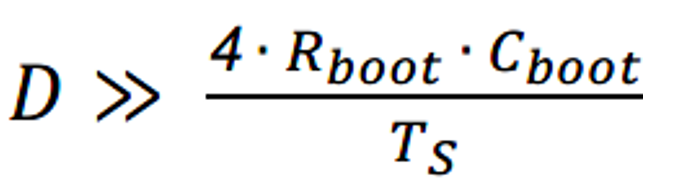

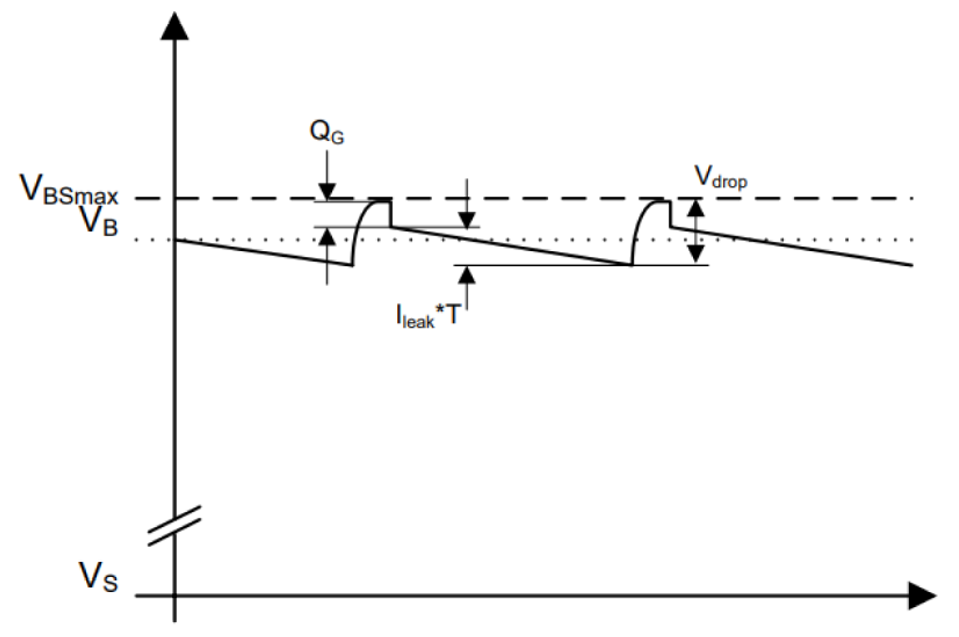

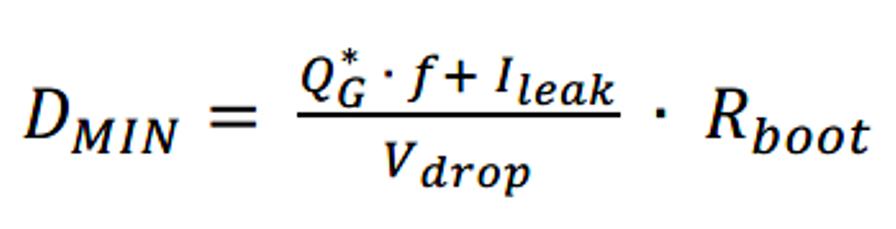

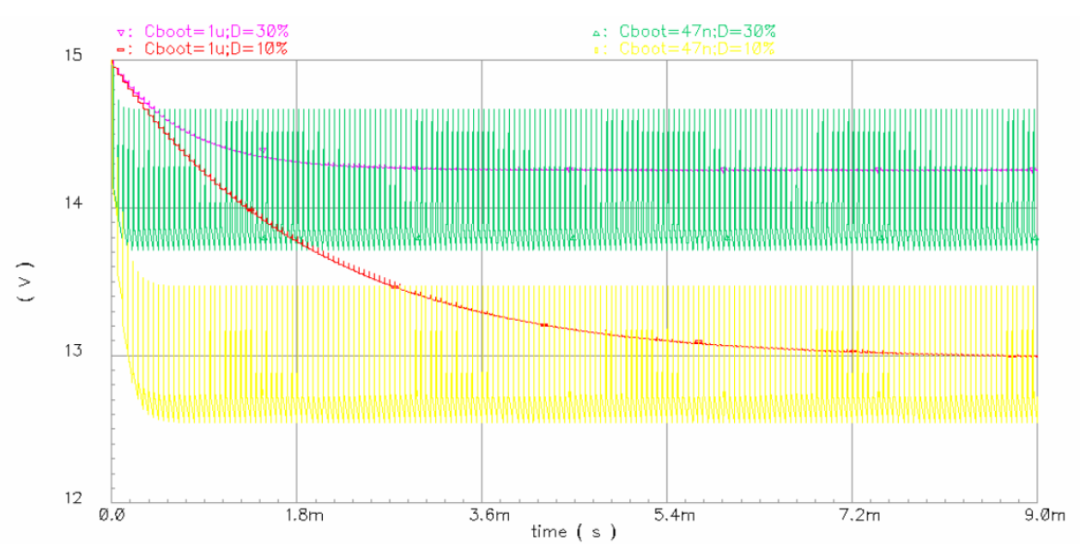

自舉電路在電平位移驅動電路應用很廣泛,電路非常簡單,成本低,而且有許多實際案例可以抄寫作業。不過,由於系統往往存在特殊或極端工況,例如設計不當調製頻率或占空比不足以刷新自舉電容器上電荷,電容上的電壓不夠,低於低電壓關閉值UVLO,這時候就出現了系統故障,嚴重時會損壞系統。上一篇《驅動電路設計(四)---驅動器的自舉電源綜述》是基於書本知識的綜述,已經提到這些問題,接下來將參考英飛凌的數據手冊和應用指南進行深入討論。本文為了簡化問題,分析固定佔空比下,也就是針對一個PWM週期內的設計。