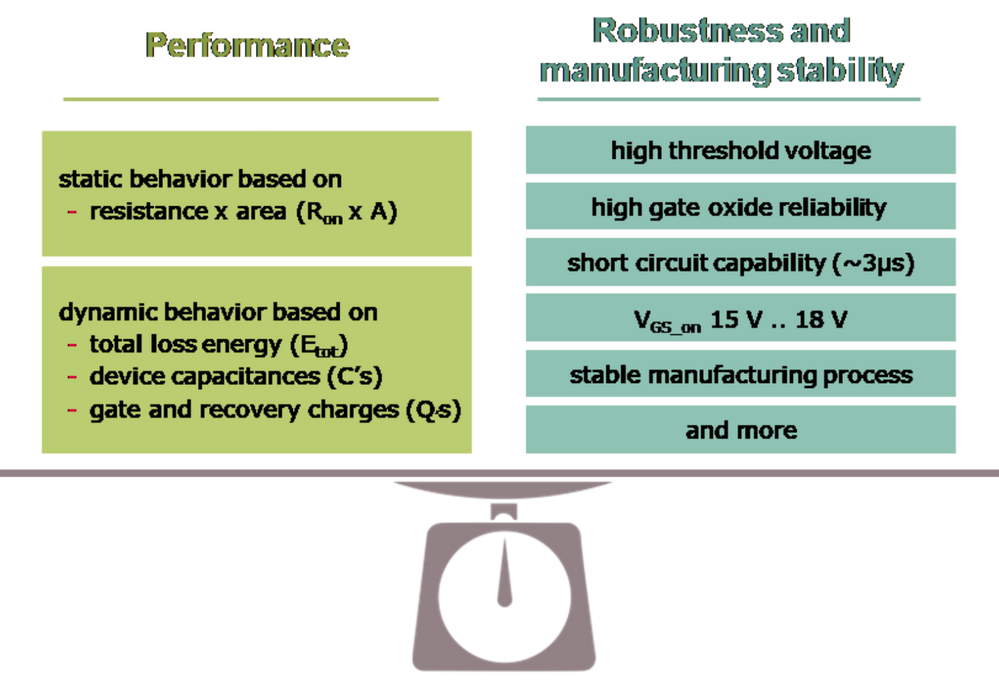

Figure 1: Robustness and manufacturing stability (right) of a SiC MOSFET have to be balanced with performance parameters (left)

The performance potential of silicon carbide (SiC) is undisputable, but designers have to master a key challenge: to determine which design approach achieves the biggest success in their application. But what are the strategies?

Advanced design activities are focusing on the field of a specific on-resistance as the major benchmark parameter for a given technology. However, it is essential for engineers to find the right balance between the primary performance indicators like resistance and switching losses, and the additional aspects relevant for real-world power electronics developments, for example sufficient reliability.

A suitable device concept should allow a certain design freedom in order to adapt to the needs of various mission profiles without significant changes in processes and layout. However, the key performance indicator will still be a low area-specific resistance of a chosen device concept, ideally in combination with the other listed parameters. Figure 1 shows a few criteria that we consider as essential, and we could add more.